### Is N w Part of

rnmr b ut ns mi<sup>™</sup>,p s visit urw bsit t <u>www. ns mi.c m</u>

DATASHEET

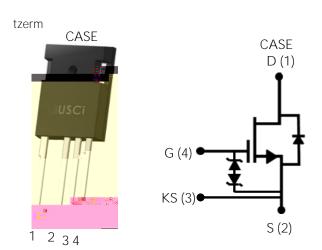

## Silicon Carbide (SiC) Cascode JFET -EliteSiC, Power N-Channel, TO-247-4L, 1200 V, 35 mohm

Rev. B, Jan 2025

## UF3C120040K4S

#### Description

United Silicon Carbide's cascode products co-package its high-performance F3 SiC fast JFETs with a cascode optimized MOSFET to produce the only standard gate drive SiC device in the market today. This series exhibits very fast switchinghas S09 0 Td(3)4

| Part Number   | Package   | Marking       |

|---------------|-----------|---------------|

| UF3C120040K4S | TO-247-4L | UF3C120040K4S |

#### Maximum Ratings

| Parameter                                                | Symbol                            | Test Conditions               | Value      | Units |

|----------------------------------------------------------|-----------------------------------|-------------------------------|------------|-------|

| Drain-source voltage                                     | $V_{DS}$                          |                               | 1200       | V     |

| Gate-source voltage                                      | $V_{GS}$                          | DC                            | -25 to +25 | V     |

| Continuous drain current <sup>1</sup>                    | I <sub>D</sub>                    | $T_C = 25^{\circ}C$           | 65         | А     |

| Continuous drain current                                 |                                   | T <sub>C</sub> = 100°C        | 47         | А     |

| Pulsed drain current <sup>2</sup>                        | I <sub>DM</sub>                   | $T_C = 25^{\circ}C$           | 175        | А     |

| Single pulsed avalanche energy <sup>3</sup>              | E <sub>AS</sub>                   | L=15mH, I <sub>AS</sub> =4.2A | 132.3      | mJ    |

| Power dissipation                                        | P <sub>tot</sub>                  | $T_C = 25^{\circ}C$           | 429        | W     |

| Maximum junction temperature                             | $T_{J,max}$                       |                               | 175        | °C    |

| Operating and storage temperature                        | T <sub>J</sub> , T <sub>STG</sub> |                               | -55 to 175 | °C    |

| Max. lead temperature for soldering, Fv⊋uol1-v⊨ou∜;1om7v | T <sub>L</sub>                    |                               | 250        | °C    |

- 1. Limited by  $T_{J,max}$

- 2. Pulse width  $t_{\rm p}$  limited by  $T_{\rm J,max}$

- 3. Starting  $T_J = 25^{\circ}C$

#### Thermal Characteristics

| Parameter                            | Symbol         | Test Conditions | Value |      |      | Units |

|--------------------------------------|----------------|-----------------|-------|------|------|-------|

|                                      |                |                 | Min   | Тур  | Max  | UTILS |

| Thermal resistance, junction-to-case | R <sub>q</sub> |                 |       | 0.27 | 0.35 | °C/W  |

#### Electrical Characteristics ( $T_J = +25$ °Cunless otherwise specified)

#### Typical Performance - Static

| $BV_{DS}$           | Min<br>1200 | Тур      | Max | V      |

|---------------------|-------------|----------|-----|--------|

|                     |             | 8        | 150 |        |

|                     |             | 35       |     |        |

| I <sub>GSS</sub>    |             | 6        | 20  | mA     |

|                     |             | 35       | 45  |        |

|                     |             | 73       |     |        |

| $V_{G(th)} \ R_{G}$ | 4           | 5<br>4.5 | 6   | V<br>W |

#### Typical Performance - Reverse Diode

$\begin{array}{cccc} & & \text{Min} & & \text{Typ} & & \text{Max} \\ I_S & & & & 65 \end{array}$

Figure 5. Typical drain-source on-resistances at  $V_{GS}$  = Figure 6. Typical transfer characteristics at  $V_{DS}$  = 5V 12V

Figure 9. 3rd quadrant characteristics at  $T_J$  = -55°C Figure 10. 3rd quadrant characteristics at  $T_J$  = 25°C

Figure 11. 3rd quadrant characteristics at  $T_J$  = 175°C Figure 12. Typical stored energy in  $C_{OSS}$  at  $V_{GS}$  = 0V

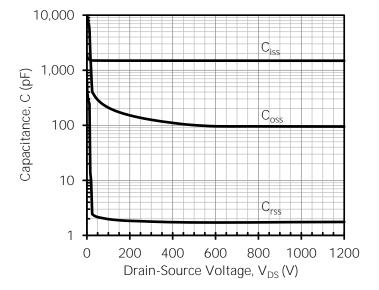

Figure 13. Typical capacitances at f = 100kHz and  $V_{GS}$  = 0V

Figure 14. DC drain current derating

Figure 15. Total power dissipation

Figure 16. Maximum transient thermal impedance

Figure 17. Safe operation area at  $T_{C}$  = 25°C, D = 0, Parameter  $t_{p}$

Figure 22. Reverse recovery charge Qrr vs. junction temperature

#### **Applications Information**

SiC cascodes are enhancement-mode power switches formed by a high-voltage SiC depletion-mode JFET and a low-voltage silicon MOSFET connected in series. The silicon MOSFET serves as the control unit while the SiC JFET provides high voltage blocking in the off state. This combination of devices in a single package provides compatibility with standard gate drivers and offers superior performance in terms of low on-resistance ( $R_{DS(on)}$ ), output capacitance ( $C_{oss}$ ), gate charge ( $Q_G$ ), and reverse recovery charge ( $Q_{rr}$ ) leading to low conduction and switching losses. The SiC cascodes also provide excellent reverse conduction capability eliminating the need for an external anti-parallel diode.

Like other high performance power switches, proper PCB layout design to minimize circuit parasitics is strongly recommended due to the high dv/dt and di/dt rates. An external gate resistor is recommended when the cascode is working in the diode mode in order to achieve the optimum reverse recovery performance. For more information on cascode operation, see www.unitedsic.com.

Disclaimer

United Sili(e)-

Information on all products and contained herein is intended for description only. No license, express or implied, to any intellectual property rights is granted within this document.

United Silicon Carbide, Inc. assumes no liability whatsoever relating to the choice, selection or use of the United Silicon Carbide, Inc. products and services described herein.

# TO-247-4L PACKAGE OUTLINE, PART MARKING AND TUBE SPECIFICATIONS

### **PACKAGE OUTLINE**

| DIM     | INCHES |     | MILLIMETERS |     |

|---------|--------|-----|-------------|-----|

|         | MIN    | MAX | MIN         | MAX |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

| P<br>P1 |        |     |             |     |

|         |        |     |             |     |

|         |        |     |             |     |

## TO-247-4L PACKAGE OUTLINE, PART MARKING AND TUBE SPECIFICATIONS

**PACKING TYPE**