## NIS5135, NIS5132 and NIS5232 Enable/Fault Pin

The enable pin of the NIS5135, NIS5132, and NIS5232 has three different logic levels. T

## AND9175/D

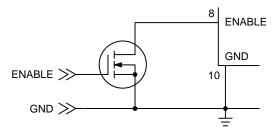

Figure 3. Circuit for Forcing a Low State on the Enable Pin

Activation of the thermal shutdown circuit provides a high signal to the internal thermal shutdown transistor to pull the enable pin out of the high state. A 1.4 V diode drop element in series with the internal thermal shutdown transistor

results in the enable pin being pulled to the intermediate or mid state. Since the mid state is below the trip point for the enable SD comparator, a high enable SD is generated and the eFuse output is disabled.

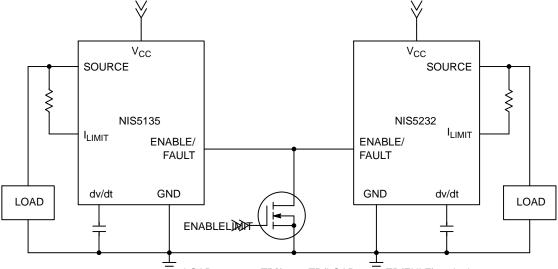

An alternate method of controlling the state of the enable pin is to tie the enable pins of multiple eFuses together. The maximum fanout (the total number of eFuses that can be connected to the pin for simultaneous shutdown) is three. A common application is a system with 5 and 12 V rails using the NIS5135 and the NIS5232 with the enable pins connected to each other as shown in Figure 4. With multiple enable pins tied together a thermal fault on one eFuse forces a mid level on all of the eFuses. This ensures full shutdown of a system under a thermal fault condition on any of the eFuses.

LOAD0 -1.2402 TD[(3795 TD(LOAD0 -1.9 TD(ENLE)65 .i5 .i5 0 0 8 4150 -1.2402 TD[(3795 T5307 444.07

## Summary

The enable pin of ON Semiconductor eFuses provides a number of features. With all eFuses, a transistor may be used to force the pin low to disable the output. In addition, it may be left floating if no control of the enable pin is required. With thermal latching eFuses, it may be brought low and then allowed to go high to reset the device. The enable pin of the NIS5135, NIS5132, and NIS5232 has a middle logic state and their enable pins may be connected to allow a common thermal shutdown. A capacitor may be connected on the NIS5112 to serve as a startup timer, while the NIS5135, NIS5132MN1, NIS5132MN2, and NIS5232 have an internal startup blanking circuit and should not have a capacitor connected from the enable pin to ground.

ON Semiconductor and are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor, "Typical" parameters with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor, "Typical" parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemity and hold ON Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, dire